熱門資訊> 正文

下一代3D封裝競賽開打:為什麼是混合鍵合?

2023-01-24 17:49

第一波芯片正在使用一種稱為混合鍵合的技術衝擊市場,為基於3D的芯片產品和先進封裝的新競爭時代奠定了基礎。

AMD是第一家推出使用銅混合鍵合芯片的供應商,這是一種先進的芯片堆疊技術,可實現下一代類似3D的設備和封裝。混合鍵合堆疊和連接芯片使用微型銅到銅互連,提供比現有芯片堆疊互連方案更高的密度和帶寬。

AMD正在使用TSMC的混合鍵合技術,TSMC也更新了其在該領域的路線圖。英特爾(Intel)、三星(Samsung)和其他公司也在開發混合鍵合技術。除了AMD,其他芯片客户也在關注這項技術。

Needham分析師Charles Shi表示:「臺積電表示,其所有高性能計算客户都可能採用其技術。」「在移動應用中,混合鍵合也在每個人的路線圖上,或者至少在每個人的雷達上。」

在半導體晶圓廠進行的一種相對較新的工藝,銅混合鍵合是一種先進的芯片堆疊技術,有望為芯片客户提供一些競爭優勢。可以肯定的是,芯片堆疊並不是什麼新技術,多年來一直在設計中使用。新的是混合鍵合可以實現近單片3D設計。

其實大多數芯片不需要混合鍵合。對於封裝而言,混合鍵合主要用於高端設計,因為它是一項涉及多項製造挑戰的昂貴技術。但它為芯片製造商提供了一些新的選擇,為下一代3D設計、存儲立方體或3D DRAM以及更先進的封裝鋪平了道路。

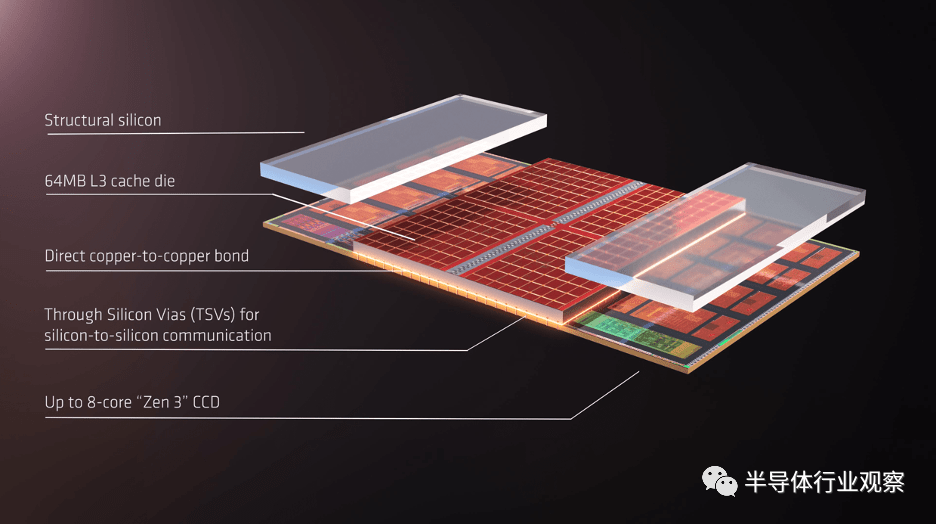

有幾種方法可以開發這些類型的產品,包括Chiplet模型。對於芯粒,芯片製造商可能在庫中有一個模塊化芯片菜單。然后,客户可以混合和匹配這些芯片,並將它們集成到現有的封裝類型或新架構中。在這種方法的一個例子中,AMD堆疊了兩個內部開發的芯粒——一個處理器和一個SRAM 芯片,形成了一個 3D封裝,在頂部結合了一個高性能 MPU 和高速緩存,並使用混合鍵合連接各個die。

還有其他實現chiplet的方法。傳統上,爲了改進設計,供應商會開發一個片上系統(SoC),並在每一代設備上集成更多的功能。這種芯片縮放方法變得越來越困難和昂貴。雖然它仍是新設計的一種選擇,但Chiplet正逐漸成為開發複雜芯片的一種選擇。

使用芯粒,大型SoC被分解成更小的dies或IP塊,並重新聚合成一個全新的設計。從理論上講,芯粒方法以更低的成本加快了上市時間。混合鍵合是實現該技術的眾多要素之一。

圖 1:AMD的3D V-Cache技術將緩存堆疊在處理器上。

封裝格局

Chiplets本身並不是一種封裝類型。它們是包含異質集成的方法的一部分,在這種方法中,複雜的dies被組裝在一個先進的封裝中。

IC封裝本身就是一個複雜的市場。據最新統計,半導體行業已經開發了大約 1,000 種封裝類型。細分封裝市場的一種方法是按互連類型,包括引線鍵合、倒裝芯片、晶圓級封裝 (WLP) 和硅通孔 (TSV)。互連用於將封裝中的一個芯片連接到另一個芯片。

雖然存在提高封裝密度的推動力,但其中許多設備仍基於舊技術,例如引線鍵合和倒裝芯片。在倒裝芯片中,基於焊料材料的微小銅凸點在芯片頂部形成。然后將該設備倒裝並安裝在單獨的模具或板上,這樣凸起就會落在銅墊上,形成電氣連接。在倒裝芯片中,芯片上的凸點間距範圍為300μm ~ 50μm。凸距指的是裸片上相鄰凸點之間的給定空間。

「不過目前140μm到150μm的粗間距封裝仍然是主流,而且短期內不會改變,」 QP Technologies母公司Promex首席技術官Annette Teng説。

與此同時,WLP 工藝用於製造扇出封裝,這最初是一種相對粗糙的技術。OSAT現在正致力於通過縮小線和空間並在其頂部添加支柱和其他3D結構來增加扇出的密度。

「(扇出)代表了智能手機和其他移動應用的一種重要的大容量小型化封裝類型,」 ASE研究員 William Chen 説。「我們還有一個充滿活力的創新領域,服務於高性能計算、人工智能、機器學習等領域。」

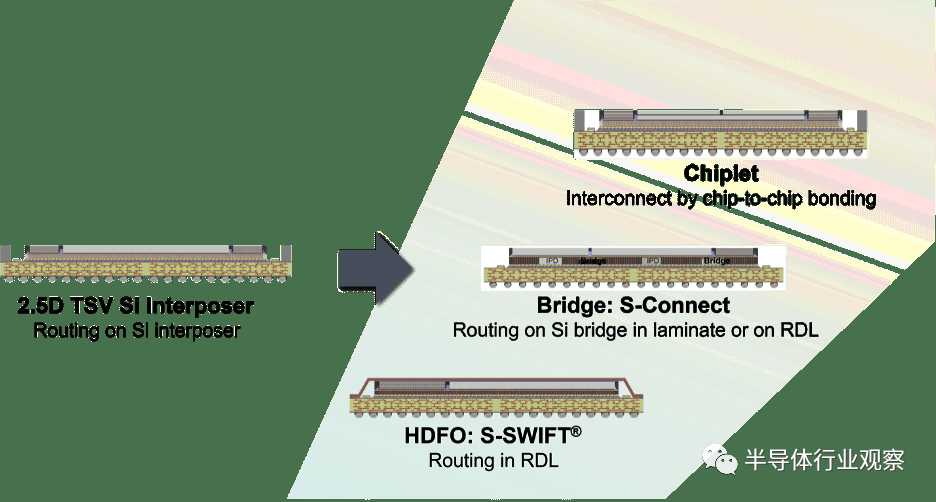

同時,2.5D 越來越成為數據中心等高性能應用的主流,而真正的3D封裝纔剛剛起步。對於 2.5D,裸片堆疊或並排放置在包含TSV的中介層之上。TSV 提供從裸片到電路板的電氣連接。

圖 2:2.5D 封裝、高密度扇出 (HDFO)、橋接封裝和Chiplet示例

2.5D 解決了幾個問題。在許多系統中,處理器、DRAM和其他設備都放在板上。數據在處理器和DRAM之間移動,但有時這種交換會導致延迟和功耗增加。作為迴應,許多高端系統將2.5D封裝與 ASIC 和 HBM 結合在一起。這允許將內存移動到更靠近處理功能的位置,從而實現更快的吞吐量。

這些封裝選項中的許多都可以支持Chiplet,裸片可以根據芯片製造商的需求進行組合。Brewer Science 高級項目經理 Xiao Liu 表示:「可以通過使用具有最佳性能/成本工藝節點的最佳處理器組件來優化系統。」

Chiplet代表了範式轉變。「這種範式轉變使封裝級的晶體管密度高於芯片級,同時還允許混合器件,每個器件都在相對於其獨特功能的最佳節點上單獨製造,異質地集成到一個通用封裝中,以提高性能並減少尺寸、重量和功率。未來將是系統級集成和優化,」i3 Microsystems 副總裁兼總經理 Brian Sapp 説。

使用芯粒方法,供應商開發了類似 3D 的架構。例如,英特爾推出的 3D CPU 平臺。在一個封裝中結合了一個10nm處理器內核和四個22nm處理器內核。

在人工智能和其他應用的推動下,所有高端產品都在增長。「AI涉及高性能計算 (HPC)。我們看到對與AI或HPC應用相關的倒裝芯片BGA的大量需求。這還包括2.5D、3D 或高密度扇出,」 JCET的首席技術官 Choon Lee 説。

這些封裝中的每一個都使用一種或多種不同的製造工藝。大多數高級封裝的共同點是互連技術。在這種情況下,它決定了您如何堆疊和接合封裝中的die。

英特爾的3D CPU、HBM 和其他芯片使用微小的銅微凸塊作為封裝中的互連方案,以及倒裝芯片工藝。使用HBM,在 DRAM 芯片的每一側形成微小的銅凸點。然后將這些芯片上的凸點粘合在一起,有時使用熱壓粘合 (TCB)。在操作中,TCB系統獲取die、對齊它們,並使用力和熱鍵合芯片。

如今,最先進的微凸塊採用40μm間距,相當於20μm至 25μm 的凸塊尺寸,芯片上相鄰凸塊之間的間距為 15μm。在研發方面,供應商正在研究凸點間距超過 40μm 的設備。在這里,客户有一些選擇。首先,他們可以使用現有的微凸塊開發芯片。基本上,基於焊料的微凸塊從今天的 40μm 間距延伸到 10μm,這些方案在這些地方已經失去了動力。

「在微小的焊料凸塊上管理小塊焊料帽有其自身的可用焊料質量分佈。在某些時候,這些將不可靠,」 Amkor高級封裝開發和集成副總裁 Mike Kelly 説。「在 20μm 和 10μm 之間的某個地方,客户將跳轉到混合方法。它有很多優點,裸片之間的功率很低,電信號路徑非常好。」

在混合鍵閤中,裸片使用微小的銅對銅互連而不是凸塊連接。對於封裝,混合鍵合的起點是 10μm 間距及以上。

微凸塊和混合鍵合都是可行的選擇。客户可以根據應用程序使用一種或另一種包裝。

為什麼要混合鍵合?

混合鍵合併不新鮮事物。多年來,CMOS 圖像傳感器供應商一直在使用它。爲了製造圖像傳感器,供應商在工廠中處理兩個不同的晶圓:第一個晶圓由許多芯片組成,每個芯片由一個像素陣列組成;第二個晶圓由信號處理器芯片組成。

然后,使用混合鍵合,將晶圓與μm級的銅對銅互連鍵合在一起。晶圓上的die隨后被切割,形成圖像傳感器。

這個過程與封裝幾乎無異。但對於封裝,混合鍵合涉及一系列不同的組裝挑戰,這就是為什麼它直到近年才投入生產。

然后,在研發方面,競技場有幾個發展。例如,Imec使用微凸塊和混合鍵合開發了所謂的 3D-SoC。在 3D-SoC 中,您可以堆疊任意數量的芯片,例如邏輯上的內存。為此,您將內存和邏輯芯片共同設計為單個 SoC。

混合鍵合實現了這些設備中最先進的互連。「爲了實現這樣的3D-SoC電路,3D互連間距需要進一步擴大,超越目前的最先進水平。我們目前的研究已經證明了在7微米間距實現這種互連的可行性,用於模對模堆疊,700納米間距用於die-to-die,」Imec的高級研究員、研發副總裁兼3D系統集成項目主任Eric Beyne在IEDM的一篇論文中説。

儘管如此,AMD正在使用臺積電的混合鍵合技術,稱為SoIC。據AMD稱,與微凸塊相比,臺積電的技術提供了超過 200 倍的連接密度和 15 倍的互連密度。AMD總裁兼首席執行官 Lisa Su 表示:「與其他競爭方法相比,這種方法每個信號的功耗不足三分之一,從而實現了更高效、更密集的集成。」

同時,在IEDM 2021會議上,臺積電副總裁 Douglas Yu提供了有關該公司 SoIC 路線圖的更多詳細信息。這為客户概述了混合鍵合凸點間距縮放路徑。

在 SoIC 路線圖上,臺積電以 9μm 的鍵距開始,並已上市。然后,它計劃引入 6μm 間距,隨后是 4.5μm 和 3μm。換句話説,該公司希望每兩年左右推出一次新的鍵合間距,每一代都提供70%的規模提升。

有幾種方法可以實現SoIC。例如,AMD設計了一款基於7nm的處理器和SRAM,由臺積電代工。然后,臺積電使用 SoIC 以 9μm鍵合間距連接芯片。

理論上,隨着時間的推移,你可以開發出各種先進的芯片,然后用臺積電的技術在各種間距上進行鍵合。

可以肯定的是,該技術不會取代傳統的芯片縮放。相反,芯片縮放仍在繼續。臺積電和三星都在研發 5 納米邏輯工藝和 3 納米及更高工藝。

曾經,從一個工藝節點到下一個工藝節點的轉變在芯片的功率、性能和麪積 (PPA) 方面提供了顯着的提升。但是,在最近的節點上,PPA 的提升正在減少。

在許多方面,混合鍵合是提供系統提升的一種方式。「過去,大部分PPA的好處都是由硅來完成的。人們過去常常讓芯片縮放來驅動系統性能。但現在,作為引擎的芯片縮放正在失去動力,」Needham 的 Shi 説。「最終,您希望通過混合鍵合來提升整個系統級 PPA。如果你想在技術上更精確,SoIC可以説是臺積電為客户提供的可用工具包中的一個強大工具。SoIC 是某些工作負載的絕佳 PPA 助推器。」

英特爾、三星和其他公司尚未發佈他們的混合綁定路線圖。

儘管如此,從架構的角度來看,所有這一切並不像看起來那麼簡單。下一代3D封裝可能會在不同節點包含多個複雜的芯粒。一些裸片可以使用混合鍵合進行堆疊和鍵合。其他裸片將位於封裝的其他地方。因此,需要一系列技術來連接所有部分。

Promex 總裁兼首席執行官 Richard Otte 表示:「對於那些挑戰極限以開發高性能計算產品的公司來説,混合鍵合可能是必需的。」「對於二維結構和應用,芯粒可能會使用高密度方法互連,包括中介層。3D-IC 需要堆疊芯粒,因此需要TSV和銅柱,以及2D高密度互連工藝。」

還有其他挑戰。在一個封裝中,所有裸片都需要使用裸片到裸片的鏈接和接口相互通信。大多數這些芯片到芯片的鏈接都是專有的,需要有開發開放標準鏈接的舉措。「Chiplet成為新 IP的最大障礙是標準化,必須建立芯粒之間的標準/通用通信接口,才能在多個封裝供應商之間實現這一點,」Otte 説。

製造挑戰

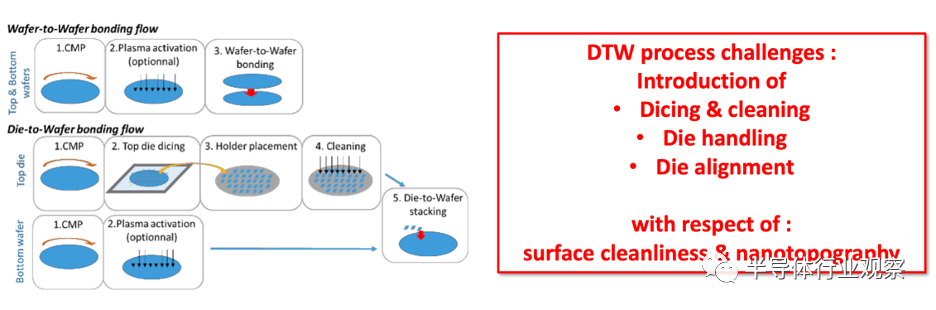

與此同時,在製造方面,兩種類型的裝配工藝使用混合鍵合——wafer-to-wafer和die-to-wafer。

在wafer-to-wafer中,芯片在晶圓廠的兩個晶圓上加工。然后,晶圓鍵合機取出兩個晶圓並將它們鍵合在一起。最后,對晶圓上堆疊的芯片進行切割和測試。

Die-to-wafer是另一種選擇。與wafer-to-wafer一樣,芯片在晶圓廠中的晶圓上加工。die是從一個晶圓上切割下來的。然后,將這些die鍵合到基礎晶圓上。最后,對晶圓上堆疊的芯片進行切割和測試。

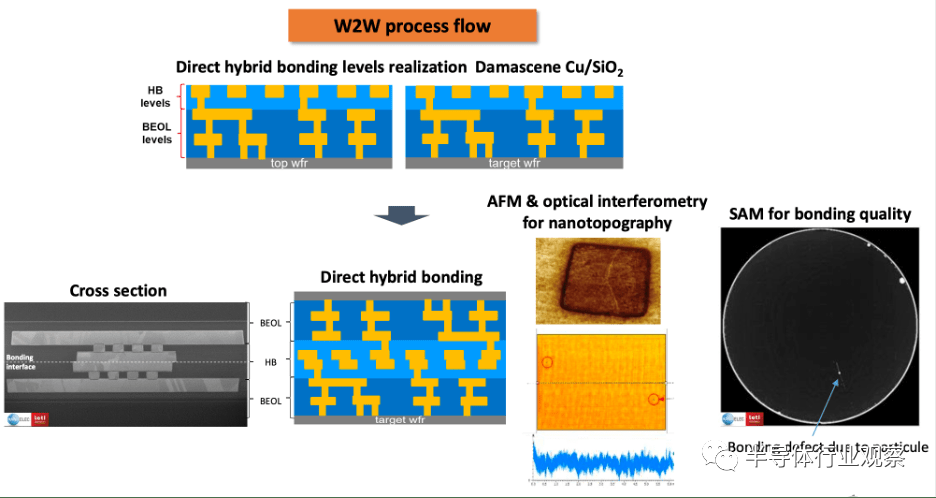

圖 3:Wafer-to-wafer流程

圖 4:Die-to-wafer流程

從一開始,擁有良好成品率的die就很重要。成品率低於標準的die可能會影響最終產品的性能。因此,預先制定良好的測試策略至關重要。

英特爾高級首席工程師 Adel Elsherbini在 IEDM 的一次演講中説:「一些芯片可能存在製造缺陷,這些缺陷最好在測試期間被篩選出來。」「但是,如果測試覆蓋率不是100%,則其中一些芯片可能會作為良好芯片通過測試。這是一個特殊的挑戰。有缺陷的芯片可能會導致最終系統良率降低,尤其是隨着芯片數量的增加。」

除了良好的測試策略外,還需要完善的流程。混合鍵合工藝發生在半導體制造廠內的潔淨室中,而不是像大多數封裝類型那樣發生在封裝廠。

在超淨潔淨室中進行此過程非常重要。潔淨室按潔淨度級別分類,潔淨度級別基於每體積空氣允許的顆粒數量和大小。通常,半導體工廠採用符合 ISO 5 級或清潔標準的潔淨室。根據 American Cleanroom Systems,在 ISO 5 級中,潔淨室中每立方米尺寸 >0.5µm 的顆粒必須少於 3,520 個。ISO 5 級潔淨室相當於舊的 100 級標準。

在某些情況下,OSAT的IC 組裝是在 ISO 7 或 10,000 級或更高級別的潔淨室中進行的。這適用於大多數封裝類型,但不適用於混合鍵合。在此過程中,微小顆粒可能會侵入流體,導致設備故障。

OSAT當然可以建造具有ISO 5潔淨室的設施,但這是一項昂貴的努力。混合鍵合需要相對昂貴的設備。此外,混合鍵合涉及半導體供應商更熟悉的幾個步驟。

在wafer-to-wafer和die-to-wafer的流程中,該過程從晶圓廠中的單個鑲嵌工藝開始。為此,在晶片的一側沉積二氧化硅層。然后,在表面上形成許多微小的通孔圖案。蝕刻圖案,在晶圓上形成大量微小的μm大小的通孔。

然后將銅材料沉積在整個結構上。使用化學機械拋光 (CMP) 系統對錶面進行平坦化。該工具使用機械力拋光表面。

CMP工藝去除銅材料並拋光表面,剩下的是微小通孔中的銅金屬化材料。

整個過程重複幾次。最終,晶圓有幾層。每一層都有微小的銅通孔,它們在相鄰層中相互連接。頂層由較大的銅結構組成,稱為焊盤。介電材料圍繞着微小的焊盤。

儘管如此,鑲嵌工藝,尤其是 CMP,具有挑戰性。它需要對晶圓表面進行精確控制。「[在晶圓上],電介質表面需要:(1) 非常光滑,以確保在連接芯片時具有強大的吸引力;(2) 非常低的形貌以避免電介質預鍵閤中的空隙或不必要的應力,」Elsherbini 在 IEDM 的一篇論文中説。

但是,在這些製程中,可能會出現一些問題。晶圓往往會下垂或彎曲。然后,在 CMP 過程中,該工具可能會過度拋光表面。銅墊凹陷變得太大。在鍵合過程中,某些焊盤可能不會鍵合。如果拋光不充分,銅殘留物會造成電氣短路。

在混合鍵閤中,標準CMP工藝可能無法解決問題。「這需要特殊的CMP處理來控制化學蝕刻與機械蝕刻的比例以及 CMP 步驟的數量,以保持電介質表面的平面度,」Elsherbini 説。CMP之后,晶圓會經過計量步驟。計量工具測量和表徵表面形貌。

「銅混合鍵合的主要工藝挑戰包括表面缺陷控制以防止空洞、晶圓級厚度和形狀計量以及納米級表面輪廓控制以支持穩健的混合鍵合焊盤接觸,以及控制頂部銅焊盤的對齊和底模,」 KLA營銷高級總監 Stephen Hiebert 説。

更多步驟

在計量步驟之后,晶圓要經過清洗和退火工藝。退火步驟激活裸片。

從這里開始,該過程可以朝兩個方向發展——wafer-to-wafer或die-to-wafer。在wafer-to-wafer中,您已經處理了第一個晶圓 (A)。然后,帶有die的第二個晶圓 (B) 經歷相同的過程(鑲嵌、CMP、計量)。

然后,使用混合鍵合將兩個晶圓 (A, B) 鍵合。芯片在晶圓上切割並進行測試。由此產生的堆疊設備類似於類 3D 結構。

與此同時,在die-to-wafer中,芯片製造商將採用第一個晶圓並激活芯片。然后,對晶圓 (A) 上的芯片進行切割和測試。

然后,第二個晶圓 (B) 經歷鑲嵌工藝,隨后是 CMP 和計量步驟。該晶圓沒有被切割並且保持完好無損。使用鍵合機,將處理后的晶圓 (A) 中的芯片堆疊並鍵合在基礎晶圓 (B) 上。

然后將芯片切割到堆疊的晶圓上並進行測試。這反過來會創建類似 3D 的設備。

對於wafer-to-wafer和die-to-wafer,供應商可以使用相同的晶圓鍵合系統。一些供應商出售這些系統,用於納米級放置精度的混合鍵合。

在操作中,裸片被放置在晶圓鍵合機內的工作臺上。處理過的晶圓被放置在鍵合機中一個單獨的晶圓臺上。從工作臺上拾取、對齊並放置在處理過的晶圓上的芯片。

此時,兩個結構的焊盤使用兩步工藝進行鍵合——首先是電介質到電介質的接合,然后是金屬到金屬的連接。「直接混合鍵合是指在 SiO2 矩陣中由銅互連組成的兩個表面的分子鍵合,」 Leti的 3D 集成項目經理 Emilie Bourjot 解釋道。「當這兩個表面在室温下緊密接觸時,範德華(van der Waals )鍵合會產生粘附力。在熱預算之后,這些鍵合會變成共價鍵合和金屬鍵合。」

粘合過程具有挑戰性。「首先要考慮的是貼裝精度和吞吐量。我們需要支持極細的間距。我們需要能夠非常準確地放置裸片,」英特爾的 Elsherbini 説。「這是通過設計優化來實現的,以確保對準基準具有非常好的可見性和對比度,同時不會佔用過多的芯片活動區域。」

鍵合機可以執行這些任務,但挑戰在於防止流動中不需要的顆粒和表面缺陷。微小的顆粒會導致焊盤中出現空洞。即使是 100nm 的顆粒侵入焊盤,也可能導致數百個連接失敗。

混合鍵合是一個複雜但可行的過程。它使新型芯片和封裝成為可能。AMD 率先採用這種方法,但其他人很快就會效仿。比賽纔剛剛開始。

本文來自微信公眾號 「半導體行業觀察」(ID:icbank),作者:MARK LAPEDUS,36氪經授權發佈。

推薦文章

提價83%需求卻暴增400%!智譜、MiniMax鎖定大模型定價權,AI Agent元年即將開啟?

港股見底了嗎?北水大舉加倉逾600億港元!大行看好4月做多窗口來臨,十大金股一圖睇全

華盛早報 | 伊朗與阿曼擬共管霍爾木茲!美股V型反轉;伊朗襲擊甲骨文、亞馬遜數據中心;港美股今日因假期休市一天

諾和諾德稱:口服版Wegovy減肥效果優於禮來GLP‑1口服藥

美股機會日報 | 特朗普粉碎停戰幻想!恐慌指數飆升12%,納指期貨跌約2%;美油期貨暴漲超9%!油氣股飆升,美國原油基金ETF漲超9%

清明休市提醒 | 港股本周五休市,下周三恢復交易;美股周五休市一天

油價上漲 此前特朗普表示伊朗衝突可能在未來幾周升級

野村:特朗普講話未能發出局勢降温的明確信號