熱門資訊> 正文

一文讀懂英偉達下一代芯片封裝技術「CoWoP」

2025-08-05 14:33

炒股就看金麒麟分析師研報,權威,專業,及時,全面,助您挖掘潛力主題機會!

(來源:網易科技)

最近市場炒得火熱的芯片晶圓板封裝(CoWoP)技術,與現有的CoWoS封裝有什麼區別?對供應鏈有何影響?商業化前景如何?

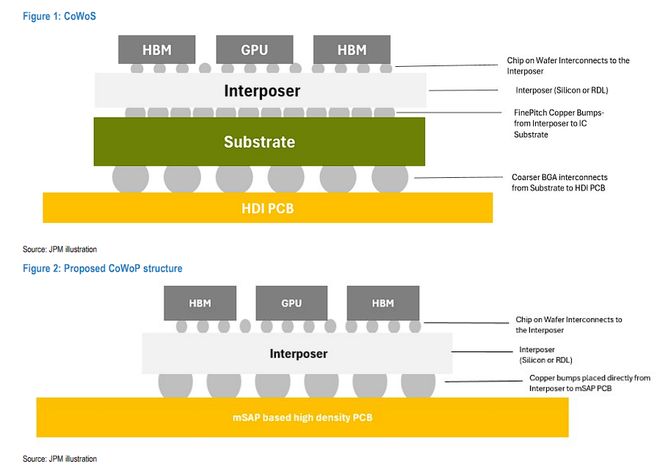

8月5日,據追風交易臺消息,摩根大通在最新研報中稱,英偉達正在探索一項革命性的芯片封裝技術CoWoP(Chip-on-Wafer-on-PCB),該技術有望替代現有的CoWoS封裝方案。

摩根大通指出,這一技術變革將利用先進的高密度PCB(印刷電路板)技術,去除CoWoS封裝中的ABF基板層,直接將中介層與PCB連接。

該行還在研報中詳細分析了"CoWoP"技術對於供應鏈的影響,認為對ABF基板廠商顯然是負面消息,卻是PCB製造商的重大機遇。

雖然,摩根大通分析師認為該技術在中期內商業化概率較低,主要受制於多重技術挑戰,但是該行在研報中強調:

CoWoP技術原理與優劣勢分析

研報稱,CoWoP代表Chip-on-Wafer-on-PCB技術路徑。在完成芯片-晶圓中介層製造步驟后,中介層(頂部帶芯片)直接安裝到PCB(也稱為平臺PCB)上,而不是像CoWoS工藝那樣綁定到ABF基板上。

該技術的潛在優勢包括:

然而,摩根大通認為,這項技術存在關鍵挑戰。目前只有蘋果公司採用mSAP或SLP PCB技術,但其節距尺寸更大,PCB板面積更小,因此將此技術擴展到具有更高載流能力的大型GPU仍然是技術和運營挑戰。

供應鏈影響:IC基板負面衝擊顯著、PCB製造商的重大機遇

摩根大通在研報中稱,對ABF基板廠商而言,這顯然是負面消息,因為基板附加值可能會大幅減少或完全消失,更復雜、精細節距的信號路由將轉移到RDL層(中介層),而高端PCB層承擔封裝內路由步驟。

摩根大通認為,對於PCB製造商,是一個重大機遇高速。研報指出:

因此,該行認為,具備先進mSAP能力以及基板/封裝工藝深度知識的公司將更有優勢。

中期內商業化概率較低,無礙英偉達創新領導力持續強化

摩根大通分析師認為,由於多重技術挑戰,CoWoP中期內商業化的概率仍然較低。

歷史上,更高的I/O數量和更精細的線/間距尺寸(CoWoS-L降至5微米,CoWoS-S約10微米)需要遷移到ABF基板。對於AI加速器,即使ABF基板也預計會在5/5線/間距尺寸之后失效。

PCB技術即使使用mSAP,目前也只能達到20-30微米的線/間距寬度,與期望性能相比仍存在較大差距。

據追風交易臺此前消息,大摩也表示,當前高密度互連(HDI) PCB的L/S為40/50微米,即使是用於iPhone主板的類基板PCB(SLP)也僅達到20/35微米,要將PCB的L/S從20/35微米縮小到10/10微米以下存在顯著技術難度。

此外,摩根大通認為,英偉達目前確定的路線圖(向CoWoS-L、CoPoS發展,在Cordelia Board中採用GPU插座)與CoWoP追求的新方向也相當矛盾。

供應鏈研究顯示,高附加值封裝生態系統參與者(如臺積電)參與度不高,主要集中在PCB廠商和特定的OSAT廠商,這降低了商業化的可能性。

不過,摩根大通指出,無論CoWoP是否成功量產,英偉達都通過系統級方法繼續引領數據中心AI基礎設施創新。

摩根大通稱,這種持續創新能力預計將使英偉達在未來數年內保持GPU領域的領先優勢,並在與ASIC競爭中佔據主導地位。

推薦文章

美股機會日報 | 凌晨3點!美聯儲將公佈1月貨幣政策會議紀要,納指期貨漲近0.5%;13F大曝光!巴菲特連續三季減持蘋果

美股機會日報 | 阿里發佈千問3.5!性能媲美Gemini 3;馬斯克稱Cybercab將於4月開始生產

港股周報 | 中國大模型「春節檔」打響!智譜周漲超138%;鉅虧超230億!美團周內重挫超10%

一周財經日曆 | 港美股迎「春節+總統日」雙假期!萬億零售巨頭沃爾瑪將發財報

從軟件到房地產,美國多板塊陷入AI恐慌拋售潮

Meta計劃為智能眼鏡添加人臉識別技術

危機四伏,市場卻似乎毫不在意

財報前瞻 | 英偉達Q4財報放榜在即!高盛、瑞銀預計將大超預期,兩大關鍵催化將帶來意外驚喜?