熱門資訊> 正文

決戰2nm,臺積電再曝新進展,三星還追得上嗎?

2022-06-16 13:05

芯東西6月15日報道,6月15日,據日經亞洲報道,日本將和美國合作,最早於2025年在日本啟動2nm製程國內製造基地。日經亞洲稱,2nm製程的芯片可以用於量子計算機、數據中心和智能手機等產品,甚至可以決定軍事裝備的性能,與國家安全直接相關。

儘管日本和美國計劃合作攻關2nm芯片,但具備量產5nm以及下製程實力,且明確提出了2nm路線圖的晶圓代工廠僅有中國臺灣晶圓代工龍頭臺積電和韓國芯片巨頭三星電子。這兩家芯片製造巨頭的2nm製程研究均已進入開發階段,並提出了明確的量產時間。

臺積電預計將在2024年年底和2025年進行2nm製程的風險試產,量產則可能會到2025年下半年或年底。三星電子則同樣計劃在2025年實現2nm的量產。

最近,臺積電和三星電子更是在2nm製程方面動作頻頻。上周五,據臺媒報道,臺積電2nm建廠計劃相關環保評審文件已送審,爭取明年上半年通過,一期項目預計2024年底前投產,投資金額高達1萬億新臺幣(約合2268億人民幣)。而三星電子的實際負責人李在鎔也訪問荷蘭光刻機龍頭ASML,據悉目標為下一代EUV光刻機,以在2nm等先進製程上取得優勢。

本文將從資本支出、技術、客户爭奪和製程節點等方面,呈現臺積電和三星電子的全方位競爭,解析這場2nm芯片戰爭。

01. 2021年競爭白熱化,臺積電、三星砸錢跑贏行業

當前,全球具備5nm及以下製程芯片製造實力的晶圓代工廠只有臺積電和三星電子兩家。雙方正展開一場以百億美元為單位、以納米乃至原子厚度為目標的先進製程競賽。

這種競賽中,臺積電和三星電子都投入了大量的資金,以在技術研發和產能擴充上佔得先機。

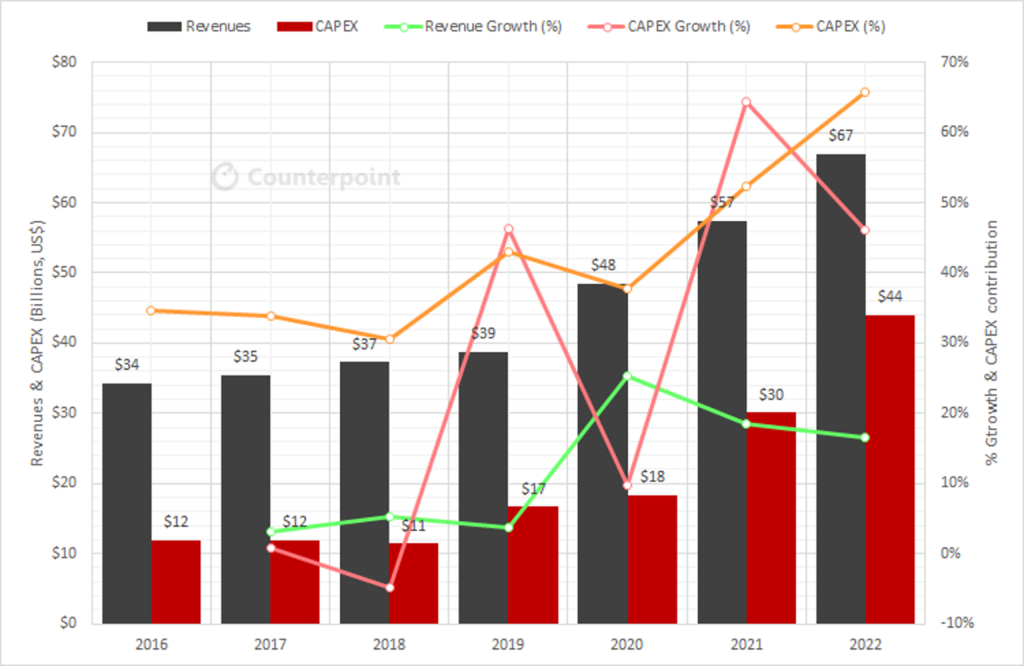

2021年,臺積電資本支出達300億美元,今年臺積電預計資本支出將達到400-440億美元(約合2687億-2956億人民幣)。在2022年的投資中,臺積電表示70%都將用於先進製程,10-20%用於特色工藝,10%用於先進封裝。

▲臺積電資本支出與營收增長對比(圖片來源:Counterpoint)

在6月8日舉辦的股東大會上,臺積電董事長劉德音預計,明年臺積電資本支出仍會達到400億美元。

如果該預測為真,這這意味着臺積電2021-2023年的資本支出將超過此前宣佈的3年千億美元,將達到1100億美元-1140億美元之間(約合7391億-7660億人民幣)。

市場分析公司Counterpoint稱,臺積電高額的資本支出將有很大一部分是對3nm和2nm節點產能的擴建,因為英特爾和蘋果等客户可能會在2023年后帶來較高的先進製程需求。

相比臺積電三年或超過1100億美元的大手筆,三星電子砸起錢來也不手軟。

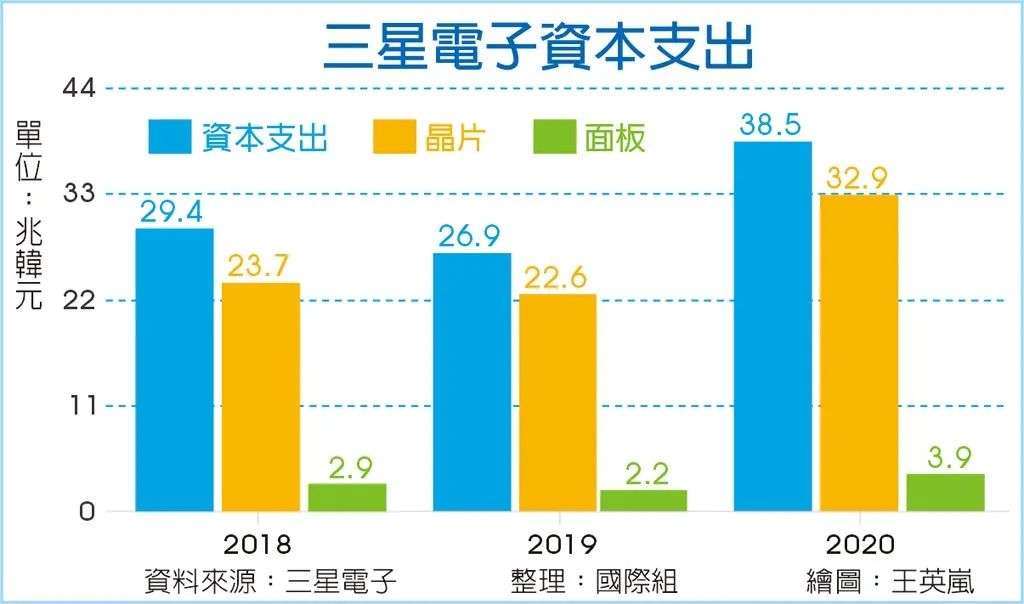

2021年,三星電子半導體與顯示總資本支出達48.22萬億韓元(約合2500億人民幣),其中用於半導體的有43.57萬億韓元(約合2300億人民幣、337億美元),主要集中在產能擴張和先進節點遷移上。

▲2018年-2020年三星電子資本支出情況(圖片來源:中國臺灣《工商時報》)

今年5月,三星電子宣佈未來5年重大投資計劃,將在2026年前,將支出增加30%以上,達450萬億韓元(約合2.4萬億人民幣,3600億美元)。據悉,雖然三星電子沒有透露各業務佔比,但分析師初步預計其在半導體領域將支出超千億美元。

總的來看,2021年,三星電子和臺積電的資本支出超過了600億美元,而在2017年前,全球半導體行業總支出不過700億美元(約合4703億人民幣)。

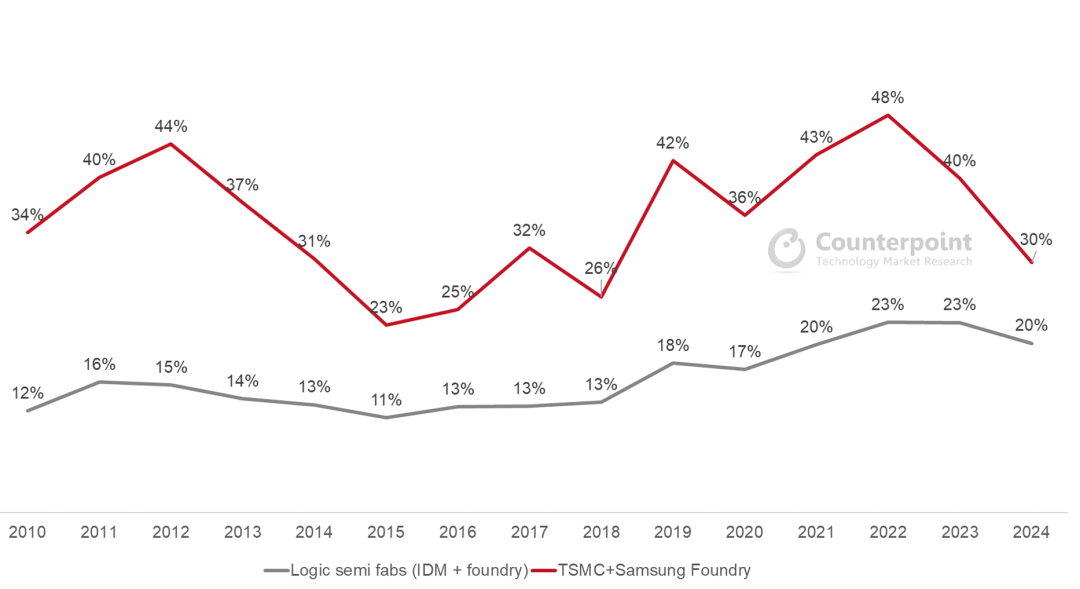

根據半導體市場分析網站IC insights的數據,2021年半導體行業資本支出合計爲1520億美元,三星電子和臺積電的資本支出佔比近40%。而且,這兩大芯片製造巨頭的資本密集度已遠遠超過整個半導體制造行業。

▲臺積電、三星電子與IDM+代工廠商資本密集度對比(圖片來源:Counterpoint)

02. 四大核心技術邁向2nm

從目前的資料來看,臺積電和三星電子的2nm之戰中,兩家公司的進展和着重點並不相同。

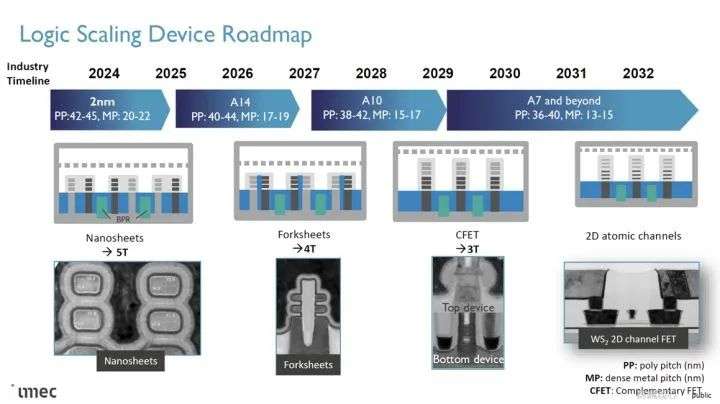

根據臺積電2021年年報,2021年臺積電已進入2nm製程研發階段,着重於測試設備的設計與實踐、光罩製作,以及硅試產,預計2025年實現2nm的量產。在去年10月的三星電子年度代工論壇上,其也宣佈進入了2nm開發階段,同樣預計2025年量產。

具體來説,在2nm節點上,臺積電和三星電子需要在晶體管結構、材料、光刻、互連等技術上進行創新。

1、新晶體管結構:三星搶先採用納米片結構,臺積電2nm棄用FinFET

芯片製程演進帶來最直接的變化之一就是晶體管結構改變。對2nm製程來説,目前的FinFET晶體管(鰭式場效應晶體管)結構已經不再適用,由於柵極氧化層過薄,會產生量子隧穿等效應,加劇晶體管漏電現象。

在去年12月的中國集成電路設計業2021年年會上,臺積電(中國)總經理羅振球稱,臺積電將在2nm節點推出納米片(Nanosheet,MBCFET)晶體管架構,並採用新的二維材料。

▲從納米片到CEFT的晶體管結構路線圖(圖片來源:IMEC)

納米片晶體管是基於納米線晶體管(Nanowire,GAAFET)的一種晶體管結構。其納米片的四個側面都是柵極,比FinFET晶體管結構能更好地控制漏電電流。

本月,美媒EE Times採訪了臺積電業務發展副總裁Kevin Zhang,稱臺積電正在評估MBCFET等基於納米片的晶體管結構。不過他提到該晶體管結構只是臺積電的選項之一,並不能確認什麼時候用於生產。

與臺積電相比,三星電子在晶體管結構上更加激進,其在3nm製程上就選用了臺積電用於2nm製程的MBCFET晶體管結構,還與IBM聯合推出了一種新的垂直晶體管架構VTFET。在同等功率下,VTFET晶體管提供了FinFET晶體管2倍的性能,而在等效頻率下,VTFET可以節省85%的功率。

▲IBM/三星電子的VTFET晶體管結構和FinFET晶體管結構對比(圖片來源:IBM)

2、新材料:二維半導體材料獲青睞

材料方面,二維材料是目前半導體行業所關注的重點。

臺積電Kevin Zhang談道,臺積電正在研究的新材料包括二硫化鎢(WuS2)和碳納米管等二維材料。這些二維材料能夠更有效地移動電子,並讓芯片實現更節能的計算。

他總結稱,由於摩爾定律的重要性正在減弱,芯片的能源效率和低功耗將成為未來的新基準。

和晶體管結構的變化類似,二維材料的應用也是爲了解決晶體管微縮后帶來的量子效應,解決漏電發熱、提升芯片能耗,並減小芯片面積。

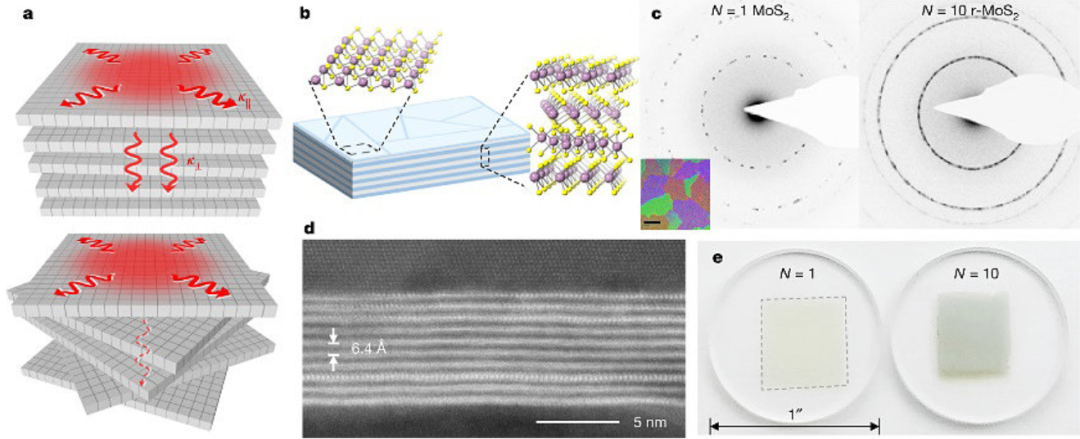

相比於當前的硅材料,二維半導體材料天生更適用於2nm及之后的先進製程,二硫化鎢和碳納米管是目前最具代表性的二維材料。

▲二硫化鎢等r-TMD化合物薄膜的結構(圖片來源:Nature)

除了晶體管結構和材料,光刻與互連技術也是實現2nm製程的關鍵。

3、新設備:聚焦High-NA EUV光刻機,三星李在鎔親自到訪ASML

在光刻方面,臺積電年報寫道,其正在提升極紫外(EUV)光刻機的應用、降低材料缺陷並增進平坦化能力以支援2nm的製程開發。

對於EUV光刻機,新的高數值孔徑(High-NA)光刻機被視作2nm製程的關鍵。

IMEC(比利時微電子研究中心)與荷蘭光刻機巨頭ASML共同開設了一個聯合High-NA實驗室,對High-NA EUV光刻機進行攻關。

▲ASML Twinscan EXE:5000系列High-NA EUV光刻機(圖片來源:ASML)

如果新一代EUV光刻機研發成功,其提升將比光刻機從乾式轉向浸沒式還要大。

根據IMEC的數據,從乾式到浸沒式,光刻波長193nm的ArF光刻機的孔徑大小相當於增加了45%,而EUV光刻機的數值孔徑從0.33NA變為0.55NA,其孔徑大小增加了67%,有望實現8nm的分辨率。

下一代EUV光刻機也是三星電子攻關2nm製程的關鍵。本月初,三星集團實際控制人、三星電子副會長李在鎔到訪荷蘭,ASML是其中關鍵一站。有業內人士分析,李在鎔拜訪ASML的主要目的之一就是採購下一代EUV光刻機,從而在先進製程上佔據優勢。

此外,ASML和IMEC也和光刻膠供應商以及光刻計量設備供應商共同進行材料和光學計量上的研究。

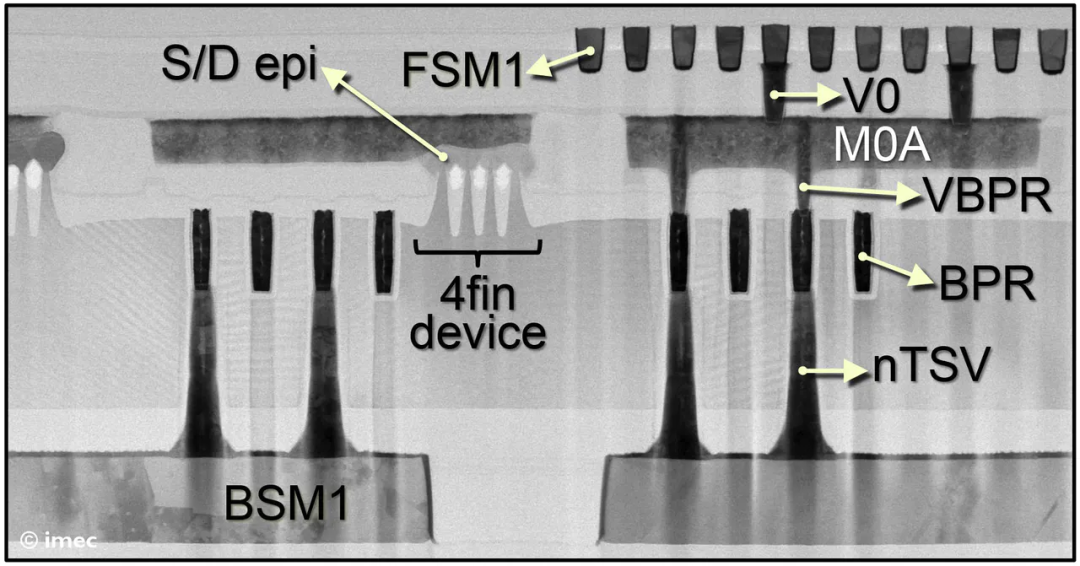

4、新封裝技術:互連是重點,IMEC新發背面供電關鍵研究

先進封裝方面,隨着芯片製程演進和晶體管結構的改變,新的互連技術被業內視作2nm製程中降低整體電阻和RC延迟的關鍵。

昨日,IMEC在2022年IEEE VLSI技術和電路研討會研討會上,展示了通過納米硅通孔(nTSV)在埋地電源軌(BPR)上的進行背面供電。

▲IMEC納米硅通孔研究示意圖(來源:IMEC)

IMEC稱,這是未來基於2nm製程的2.5D和3D芯片的關鍵技術,該方案將在系統層面提高芯片整體供電性能,避免受到功率密度提升和電源電壓下降的影響。

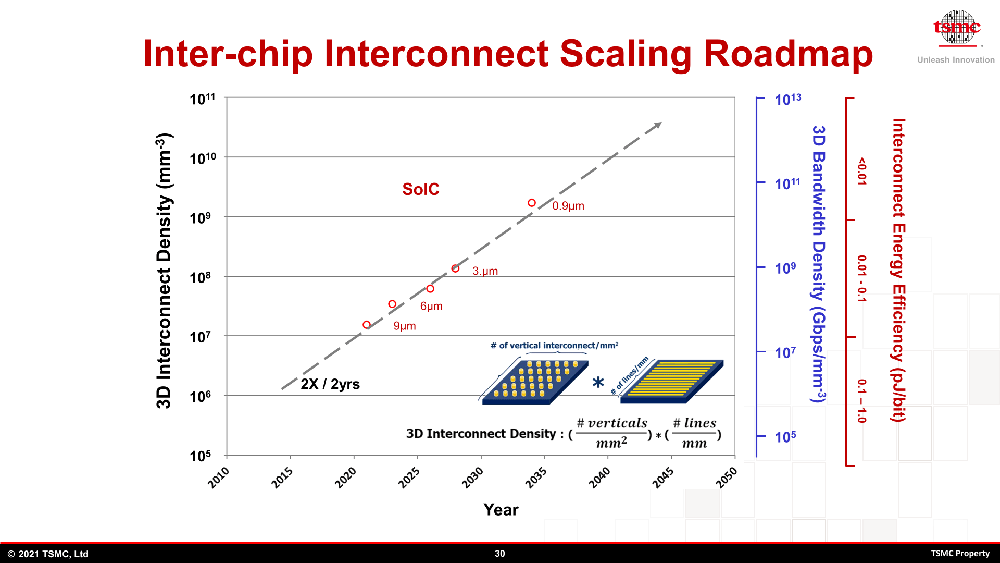

臺積電和三星電子也十分看重互連技術對先進製程的影響,均在各自的先進封裝技術中。臺積電的芯片互連技術路線圖更是拓展到了2035年,要在2035年前實現1μm以內的SoIC互連。

▲臺積電SoIC互連路線圖

03. 三星內鬥、良率問題引發關注,先進製程客户正流失

在芯片代工江湖中,蘋果從三星電子轉投臺積電成就兩大科技巨頭同盟的故事,一直被人所津津樂道,也凸顯了頭部客户對晶圓製造玩家的重要性。

根據Counterpoint的數據,2021年,蘋果、高通、三星電子、聯發科、AMD和英偉達是採用5nm製程芯片的主要芯片設計公司,這些頭部芯片設計公司也會成為臺積電、三星電子2nm製程代工的主要客户。

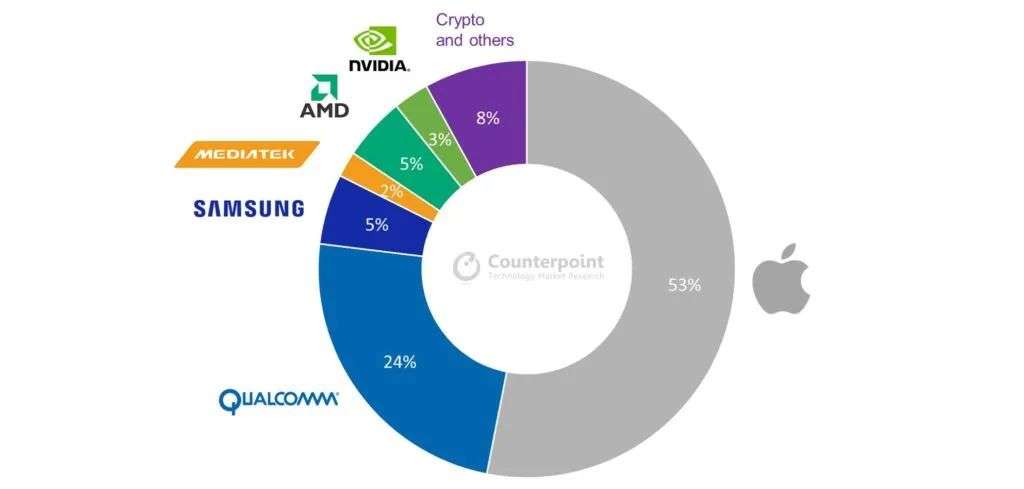

▲2021年5nm芯片出貨量份額(圖片來源:Counterpoint)

從體量上來看,蘋果佔到了2021年5nm芯片出貨量的53%,高通佔24%,三星電子、聯發科、AMD和英偉達則分別佔5%、2%、5%和3%。

當前,蘋果、聯發科、AMD是臺積電的主要客户,三星電子芯片設計部門(S.LSI)、高通和英偉達(高通和英偉達都有部分芯片在臺積電代工)的芯片主要由三星電子代工業務負責。

但三星電子代工業務在芯片良率、散熱等問題上表現不盡如人意。根據外媒SemiAnalysis的報道,由於三星電子基於4nm製程的Exynos 2200處理器良率表現十分之低,其GPU頻率從計劃的1.69GHz削減到1.49GHz,最終減少到1.29GHz。

為此,三星電子代工的大客户高通和英偉達已經協商按照芯片最終產量付費,而非按晶圓付費。

同時,三星電子內部的手機部門、芯片設計部門和代工部門配合並不默契,其芯片設計部門指責代工部門良率和規格造假,而手機部門則指責芯片設計部門的芯片方案性能不強、成本又高。

相比之下,臺積電的代工良率一直表現較好,有消息稱其2nm的風險試產良率也已超過了90%。

這種差距也讓三星電子正在失去高通和英偉達這兩個最核心的先進製程代工客户。

爲了轉向臺積電的N4工藝,高通有專門的團隊進行了數月的加緊工作,推出了基於臺積電N4工藝的驍龍8+。而根據爆料信息,英偉達的下一代遊戲顯卡(即GeForce RTX 40系列)的Ada Lovelace GPU也將採用臺積電的N4工藝,不再沿用三星電子代工。

▲英偉達GeForce RTX 30系列和GeForce RTX 40系列參數對比(圖片來源:SemiAnalysis)

如果三星電子后續的3nm製程不能實現反超,其2nm製程的市場前景並不樂觀。

此外,三星電子已經進行了多輪公司架構調整。去年12月,三星電子將原先的消費電子與移動通信兩個部門合併,並同時撤換了三個部門的三位CEO,替換爲了此前負責電視業務的韓鍾熙和子公司三星電機的社長慶桂顯。

在良率問題曝光后,三星電子半導體研發中心負責人、晶圓代工高管也由存儲部門的專家和高管所取代。

其副總裁兼NAND開發部門Song Jae-hyuk成為半導體研發中心的新負責人,存儲專家、半導體設備解決方案部門全球製造與技術設施副總裁Nam Seok-woo兼任晶圓代工製造技術中心負責人,內存製造技術中心副總裁Kim Hong-shik則負責領導代工技術創新團隊。

從人事變動來看,三星電子把存儲部門的專家和高管看作了重整邏輯芯片製造的底牌,接下來其3nm、2nm的表現或許也將決定其能否實現「2030年成為邏輯芯片製造世界第一」的目標,乃至能否繼續和臺積電競爭先進製程。

04. 結語:產能、製程兼顧,三星、臺積電2nm戰爭拉開序幕

5nm節點后,臺積電和三星電子進入了先進製程的決賽圈,誰能取得優勢,誰就能掌握半導體供應鏈的主動權,成為5G、人工智能、自動駕駛、高性能計算等領域的核心芯片供應商。

這個恰遇2020年新冠肺炎疫情全球缺芯的先進製程之戰,直接就進入了白熱化階段,三星電子和臺積電不僅要在製程工藝上一決勝負,更要擴產建廠掌握供應鏈核心地位。這對兩家公司來説,既是挑戰,也是機遇。

如今臺積電萬億新臺幣晶圓廠已進入審批流程,更在先進製程產能、客户和良率等方面取得了領先。但三星電子仍不會放棄這場逼近物理極限的戰爭,將在3nm之后和臺積電一決勝負。

本文來自微信公眾號「芯東西」,作者:高歌

風險及免責提示:以上內容僅代表作者的個人立場和觀點,不代表華盛的任何立場,華盛亦無法證實上述內容的真實性、準確性和原創性。投資者在做出任何投資決定前,應結合自身情況,考慮投資產品的風險。必要時,請諮詢專業投資顧問的意見。華盛不提供任何投資建議,對此亦不做任何承諾和保證。

推薦文章

提價83%需求卻暴增400%!智譜、MiniMax鎖定大模型定價權,AI Agent元年即將開啟?

港股見底了嗎?北水大舉加倉逾600億港元!大行看好4月做多窗口來臨,十大金股一圖睇全

華盛早報 | 伊朗與阿曼擬共管霍爾木茲!美股V型反轉;伊朗襲擊甲骨文、亞馬遜數據中心;港美股今日因假期休市一天

諾和諾德稱:口服版Wegovy減肥效果優於禮來GLP‑1口服藥

美股機會日報 | 特朗普粉碎停戰幻想!恐慌指數飆升12%,納指期貨跌約2%;美油期貨暴漲超9%!油氣股飆升,美國原油基金ETF漲超9%

清明休市提醒 | 港股本周五休市,下周三恢復交易;美股周五休市一天

油價上漲 此前特朗普表示伊朗衝突可能在未來幾周升級

野村:特朗普講話未能發出局勢降温的明確信號